ProASIC3 Flash Family FPGAs Overview

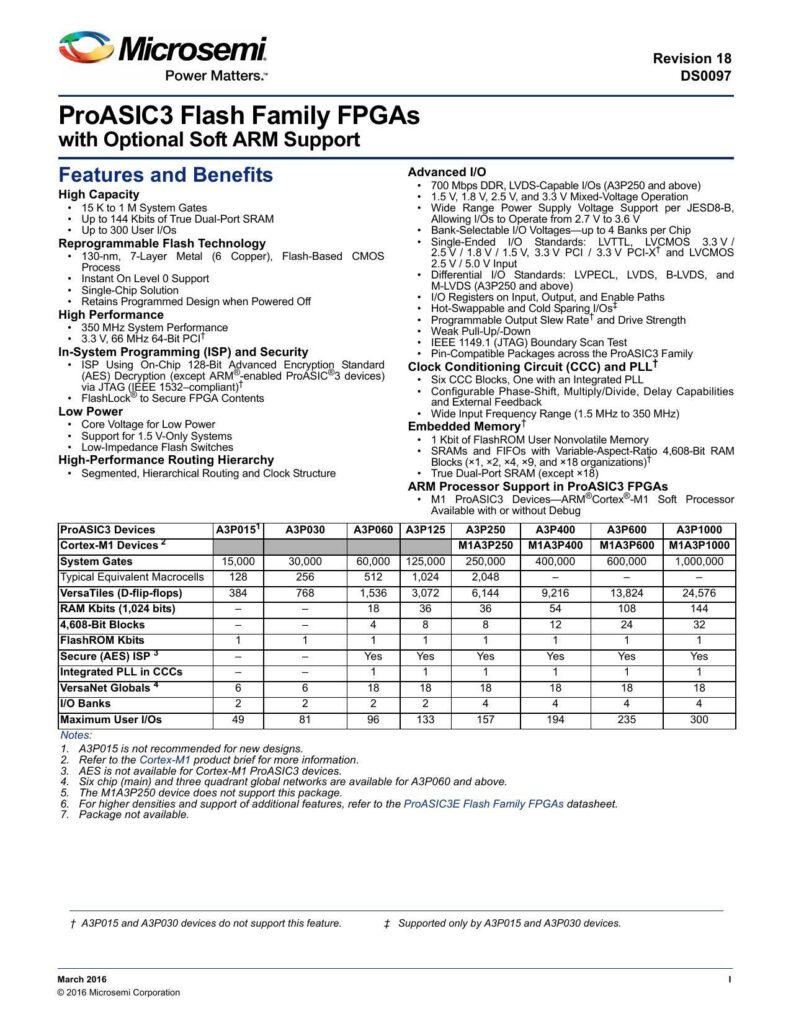

The ProASIC3 Flash Family of Field Programmable Gate Arrays (FPGAs) by Microsemi offers advanced system integration and performance features suitable for a wide range of applications. These FPGAs range from 15K to 1M system gates, accommodating various design sizes, and are complemented by a versatile set of I/O standards, embedded memory options, and ARM processor support in selected devices.

Key Features and Benefits

- High-Speed Interfacing: Devices in the family, starting from the A3P250 model, support interfaces up to 700 Mbps with DDR and LVDS capabilities.

- Mixed-Voltage Operation: The FPGAs operate at multiple voltage levels, including 1.5V, 1.8V, 2.5V, and 3.3V, enhancing compatibility with different system requirements.

- Dual-Port SRAM & User I/Os: Devices come with up to 144 Kbits of true dual-port SRAM and up to 300 user I/Os, with bank-selectable voltage levels for added flexibility.

- Reprogrammable Flash Technology: The FPGAs feature reprogrammable flash technology, enabling in-system programming and design retention upon power-off.

- Diverse I/O Standards: These FPGAs support multiple single-ended and differential I/O standards, including LVPECL, LVDS, B-LVDS, M-LVDS, LVTTL, LVCMOS, and PCI standards, for comprehensive interfacing options.

- High System Performance: With up to 350 MHz system performance, these devices are capable of high-speed operations, and they include a clock conditioning circuit and programmable phase-shift options.

- Security Features: Security measures are provided through an on-chip 128-bit AES decryption engine, and the FlashLock feature secures FPGA contents.

- Low Power & Embedded Memory: The FPGAs maintain low core voltage power consumption, and support embedded memory for 1.5V-only systems.

- ARM Cortex-M1 Processor Support: Certain devices within the family, designated as Cortex-M1 models, incorporate the ARM Cortex-M1 soft processor, available with or without debugging features.

Variants and Package Options

The ProASIC3 family includes a range of devices from A3P015 to A3P1000 with varying system gates and macrocells. They are available in several package types, including QFN, VQFP, TQFP, PQFP, and FBGA, with different pin configurations to suit various design requirements. Note that A3P015 and A3P030 devices offer specific features and packages not supported by other models, emphasizing their unique positioning within the family.

Additional Information

The datasheet emphasizes that the A3P015 model is not recommended for new designs and that the Cortex-M1 ProASIC3 devices do not support AES. For applications requiring higher densities and enhanced features, users are directed to the ProASIC3E Flash Family FPGAs datasheet. Important notes on global network availability and package support for each device variant are also provided.

References:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/a3p060-vq100/6425866151824647094/