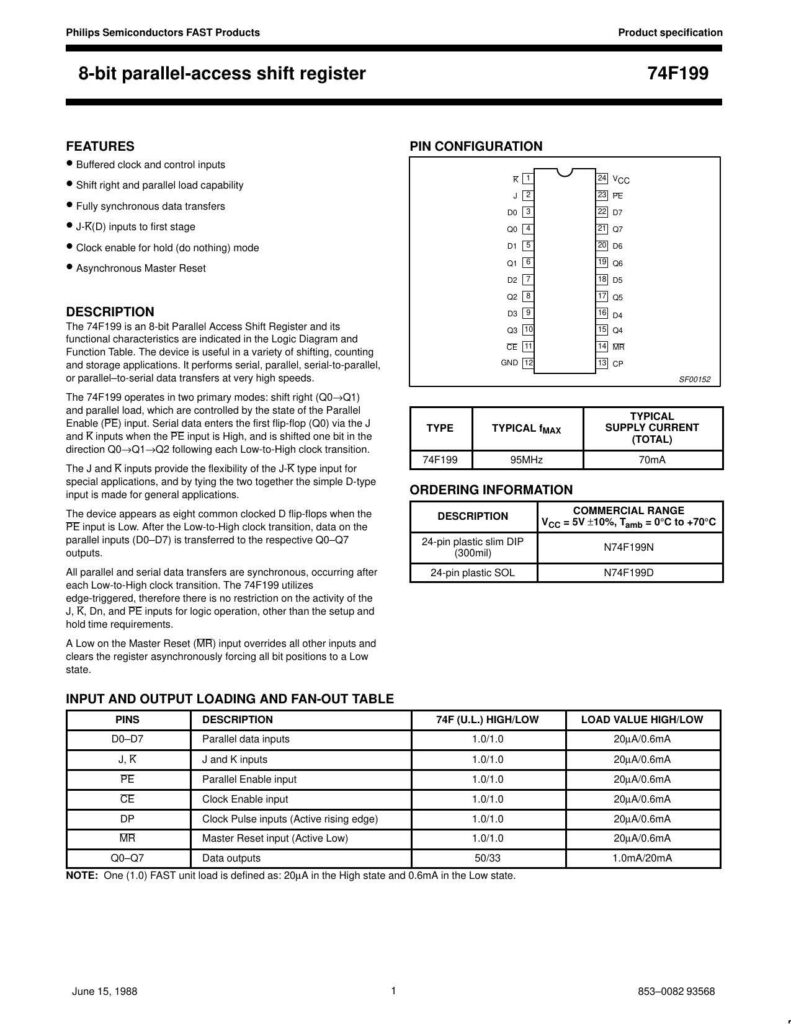

The 74F199 is a high-speed 8-bit parallel-access shift register with buffered clock and control inputs, offering shift right and parallel load capabilities.

It features fully synchronous data transfers, J-K(D) inputs to the first stage, and a clock enable for hold (do nothing) mode, as well as an asynchronous Master Reset.

Operating Modes

The device operates in two primary modes: shift right (Q0-Q7) and parallel load, controlled by the Parallel Enable (PE) input.

Key Features

Serial data enters the first flip-flop (Q0) via the J and K inputs when the PE input is High, and is shifted one bit in the direction Q0-Q7 following each Low-to-High clock transition.

The device appears as eight common clocked D flip-flops when the PE input is Low, transferring data on the parallel inputs (D0-D7) to the respective Q0-Q7 outputs after each Low-to-High clock transition.

All parallel and serial data transfers are synchronous, occurring after each Low-to-High clock transition.

Manual:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/n74f199n/3127372454576567747/