This datasheet describes synchronous register-latch mode, high-performance CMOS static random access memories (SRAMs) with 8Mb (256Kx36 or 512Kx18) and 4Mb (128Kx36 or 256Kx18) organizations.

Key features include:

Features

- Latched outputs

- Common I/O

- 0.25 micron CMOS technology

- Asynchronous output enable

- Synchronous register-latch mode of operation with self-timed late write

- Synchronous power down input

- Single differential HSTL clock

- Boundary scan using limited set of JTAG 1149.1 functions

- +3.3V power supply; ground, 2.0V max VDDQ, and 0.85V VREF

- Byte write capability and global write enable

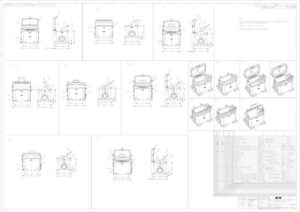

Package

7 x 17 Bump Ball Grid Array Package with SRAM JEDEC Standard Pinout and Boundary SCAN Order

Manual:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/ibm0436a4aclab-37/4764135282460349981/