Description

The ZL10313, released by Zarlink Semiconductor in November 2004, is a high-performance QPSK/BPSK demodulator designed for digital satellite television transmissions adhering to the European Broadcast Union (EBU) ETS 300 421 standard and DirecTV specification for DSS. It operates on analogue and Q signals received from a tuner and is capable of handling symbol rates up to 45 MSps. The device features on-chip digital filtering, dual-ADC, and a high-speed scanning mode for automatic symbol rate and code rate acquisition. With an integrated Forward Error Correction (FEC) and descrambling system, the ZL10313 outputs MPEG2 or DSS transport stream data packets.

The demodulator streamlines development by offering a high-level software interface, enabling minimal programming effort for control. It possesses a dual-ADC that operates at 60 or 90 MHz, an automatic spectral inversion resolution, and an impressive LNB frequency tracking of up to +22.5 MHz. Additionally, it supports DiSEqC™ v2.2 which allows full control of LNB, dish, and other system components.

The ZL10313 is offered in a compact 64-pin LQFP package and is available with options for Bake & Drypack. Pb-Free Matte Tin versions and dies in wafer form are provided as well, reflecting its compliance with environmental manufacturing standards. The temperature operational range is specified from 0°C to +70°C.

Applications

The device caters to various applications, including satellite receivers that are DVB 45 MSps and DSS 20 MSps compliant, Single Master Antenna TV (SMATV) transmodulators, and satellite PC configurations. These applications benefit from the device’s capabilities for ensuring high-quality satellite signal reception and decoding.

Key Features and Functional Block Diagram

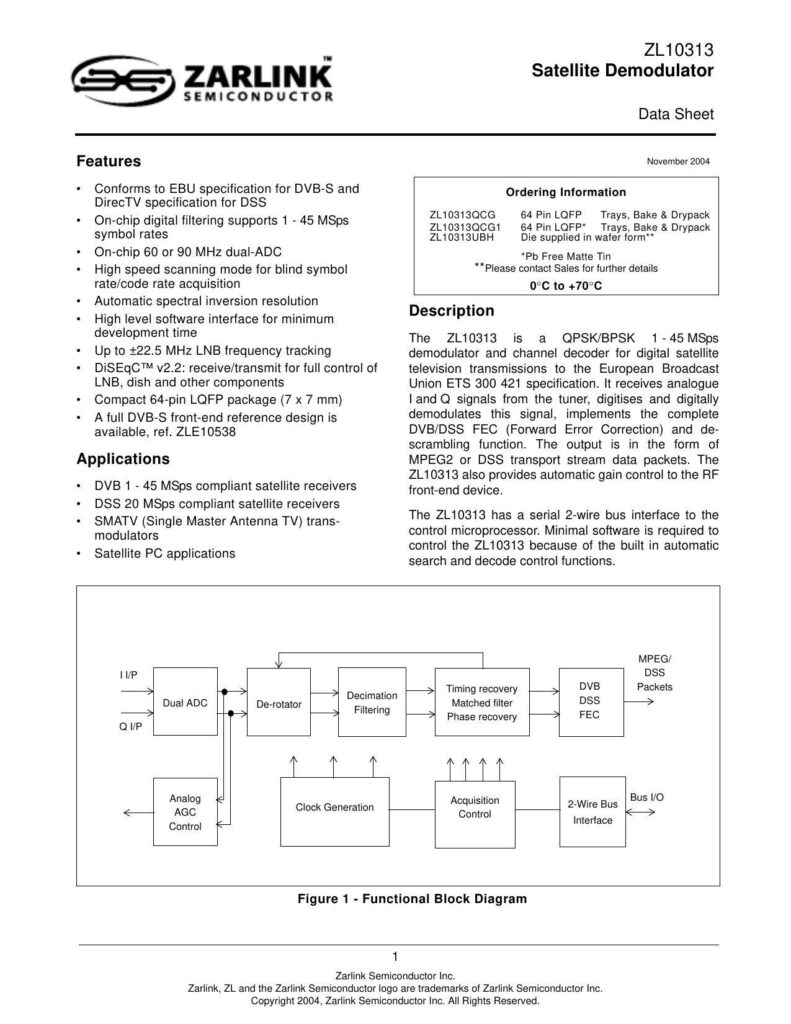

Notable features include an end-to-end DVB-S front-end design, fast tracking for both LNB frequency and automatic gain control to the RF front-end. The ZL10313’s internal architecture is complex, with specific blocks for different tasks, such as matched filtering, phase recovery, de-rotation, decimation, and more, which all streamline the process from analog signals to digital output with precise control and minimum interference.

The integrated 2-wire bus interface simplifies communication between the demodulator and a control microprocessor, with built-in functions for automatic search and decode. This reduces the demand for extensive software control, allowing for easier integration into existing systems.

As per the functional block diagram provided, the ZL10313 contains multiple components that handle specific tasks in signal processing. These include timing recovery, phase recovery, and FEC for DVB/DSS, among others. The diagram illustrates how the input signal undergoes various transformations and processing steps, orchestrated by the demodulator’s automatic control systems, before being output as a digital signal suitable for a viewer’s television or satellite PC application.

References:

Download: ZL10313 Satellite Demodulator Data Sheet

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/zl10313qcg1/-7972732861514897056/