Overview of Zilog Z80 CPU Product Specification

The Zilog Z80 CPU is positioned as a high-performance processing unit with robust features designed for a broader range of applications. The CPU stands out with its extensive instruction set, which includes 158 instructions with compatibility for the 8080A instruction set.

Key Features

The Z80 offers a comprehensive ecosystem consisting of:

- Vectorized interrupt systems that support daisy-chaining and priority schemes.

- Dual general-purpose and flag registers sets with versatile capabilities.

- Two 16-bit index registers for advanced data management.

- Three modes of maskable interrupts for flexible operational environments.

- An on-chip dynamic memory refresh counter for consistent performance.

Additionally, the CPU facilitates a range of performance and power needs with both NMOS and CMOS versions. The NMOS options include 4 MHz, 6 MHz (also operable at 6.144 MHz), and 8 MHz models, while CMOS variations range from 6 MHz up to 20 MHz.

Physical Configuration and Usability

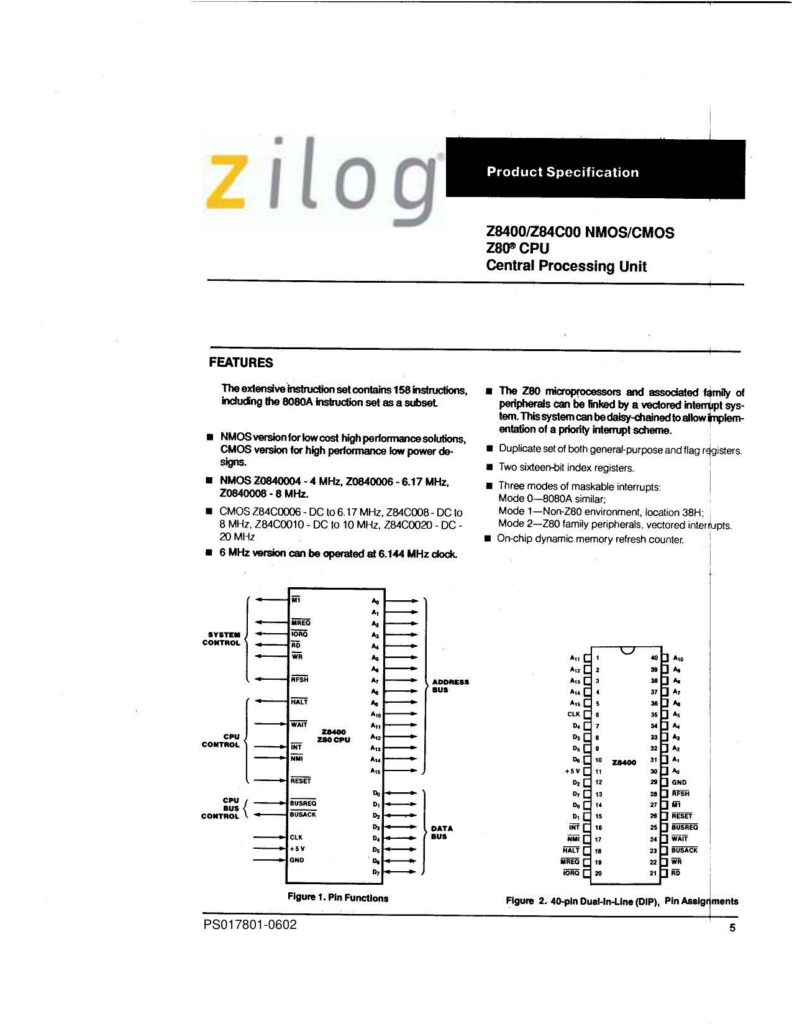

Figures 1 and 2 on the datasheet present the pin functions and assignments for the 40-pin Dual-In-Line (DIP) and the 44-pin configurations, which cater to the 84C00 CMOS version of the Z80 CPU. The pin layouts are designed to support efficient system integration.

General Description

The Zilog Z80 CPU is a fourth-generation microprocessor that outpaces prior generations in terms of computational capability and memory efficiency. Internally, the CPU includes numerous accessible registers such as the Stack Pointer, Program Counter, two index registers, a Refresh register (counter), and an Interrupt register. These registers are complemented by a block diagram illustrating the CPU’s primary functions, including the Data Bus Interface, Instruction Decoder, Internal Data Bus, ALU, Register Array, and various control and timing logics.

The ease of incorporation into systems is highlighted by the CPU’s requirement for only a single +5V power source and fully decoded output signals. The datasheet concludes by emphasizing the Z80 CPU’s support from an extensive array of peripheral controllers, outlining how this facilitates a smoothly functioning integrated environment.

Additional Information

Detailed information on the I/O controller family, registers, instruction set, interrupts, daisy chaining, and CPU timing can be found in the following sections of the full datasheet.

References:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/z84c0010veg/-7211624304220214330/