Overview of ZiLc&S Z80 DMA

The ZiLc&S 28410/284C10 datasheet provides detailed information on the NMOS/CMOS Z80 DMA (Direct Memory Access) Controller, designed to optimize data transfer processes within computer systems. This DMA controller can operate in Byte-at-a-Time, Burst, or Continuous modes, with programmable cycle length and edge timing to match various port speeds. It facilitates a range of operations such as memory-to-I/O, memory-to-memory, and I/O-to-I/O transactions.

Key Features

The Z80 DMA controller includes dual port address generation with options for fixed or automatically incremented/decremented addresses. Buffered starting-address registers enable loading of a new operation without interfering with the current one, and the ability to repeat previous sequences automatically. The device ensures extensive programmability and allows the CPU to read comprehensive channel status. It comes in both NMOS and CMOS versions, with the NMOS Z0841004 catering to cost-sensitive solutions and the CMOS Z84C1006 and Z84C1008 providing low power consumption options with speed variations up to 8 MHz.

Compatibility and Integration

The datasheet emphasizes the DMA’s compatibility with the Z80 family’s standard bus-request and prioritized interrupt-request daisy chains, eliminating the need for external logic. Additionally, sophisticated and internally modifiable interrupt vectoring facilitates direct interfacing to system buses, further reducing the need for extra components.

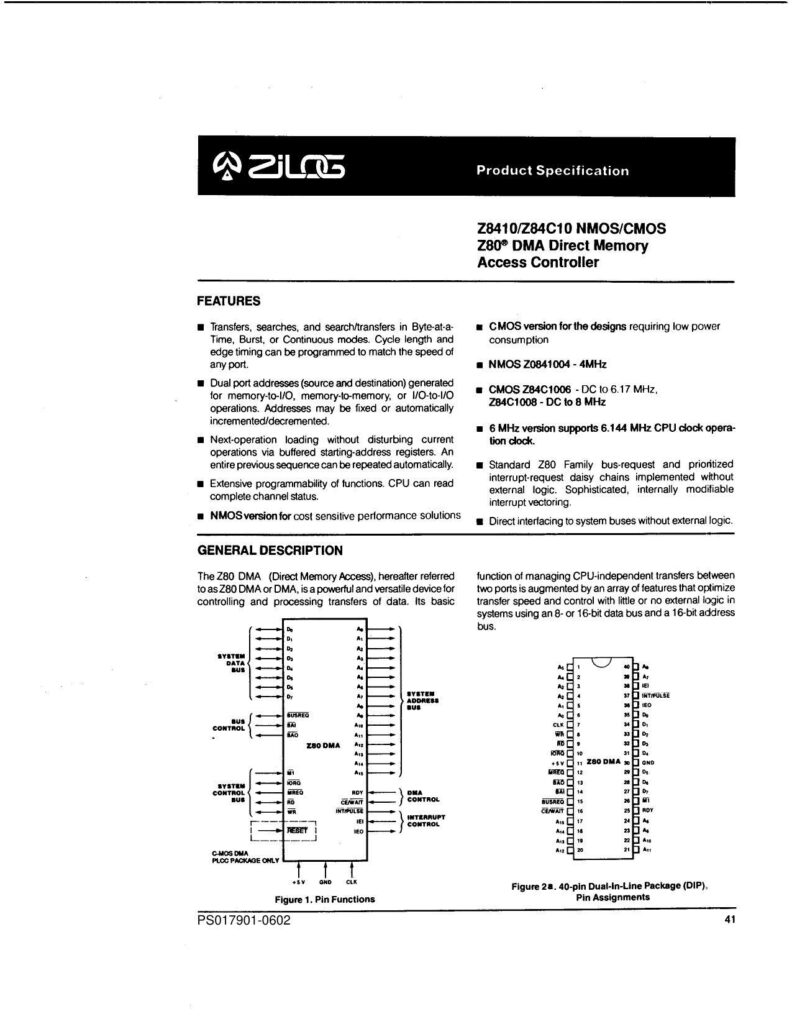

Technical Specifications and Pin Assignments

Figures provided demonstrate the 40-pin Dual-In-Line Package (DIP) and 44-Pin PLCC pin assignments for the NMOS and CMOS variants, indicating the placement of the CLK, GND, MREQ, BUSREQ and other critical pins essential for the operation and integration of the Z80 DMA into existing systems.

General Description

The Z80 DMA is tailored for 8- or 16-bit data bus systems with a 16-bit address bus. Its primary role is to manage CPU-independent data transfers between two ports. The device is lauded for its versatility in controlling data transfers with minimal external logic requirements.

In summary, the ZiLc&S 28410/284C10 datasheet provides a comprehensive guide to understanding, implementing, and leveraging the capabilities of the NMOS/CMOS Z80 DMA for efficient data transfer operations suitable for a wide range of applications.

References:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/z84c1008peg/-6183373714313409467/