Overview

The Zctel TM ACT 1 Series FPGAs datasheet presents a comprehensive look at these field-programmable gate arrays, specifying both technical details and features that make the series suitable for various high-performance applications. Designed with 1.0 micron CMOS technology and incorporating Actel’s proprietary PLICE antifuse technology, these FPGAs provide a blend of flexibility and efficiency.

Key Features

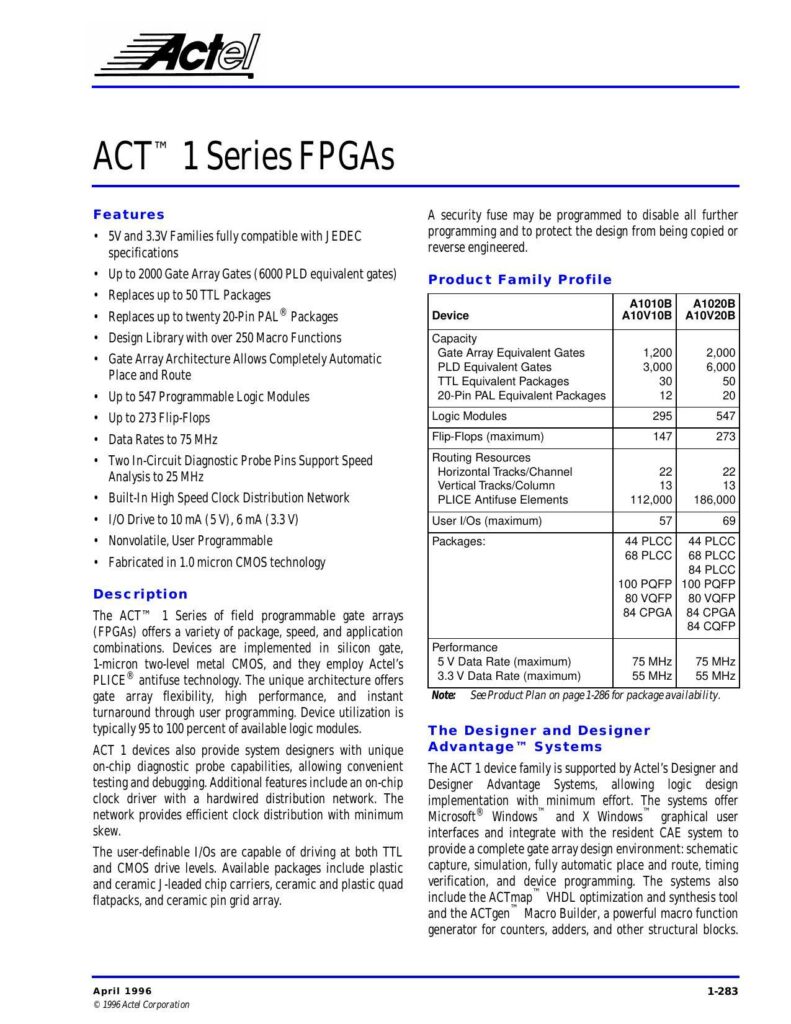

The ACT 1 Series FPGAs are notable for their compatibility with 5V and 3.3V logic levels and JEDEC specifications. Capacities range from as few as 1,200 gate array equivalent gates to as many as 6,000 PLD equivalent gates. Performance-wise, they offer data rates up to 75 MHz for 5V and up to 55 MHz for 3.3V applications.

Logic Design and Diagnostic Capabilities: Users can replace up to 50 TTL packages or twenty 20-pin PAL packages with these FPGAs, capitalizing on a design library that includes over 250 macro functions. They feature up to 547 programmable logic modules, a maximum of 273 flip-flops, and in-circuit diagnostic probe pins for speed analysis up to 25 MHz.

Gate Array Architecture: Ensures high utilization rates (typically 95 to 100 percent) of the available logic modules and supports a built-in, high-speed clock distribution network.

I/O Capabilities: The devices provide user-definable I/Os capable of driving TTL and CMOS levels, with a maximum output of 10 mA for 5V and 6 mA for 3.3V operating voltages.

Security Feature: A programmable security fuse is available to prevent further programming, protecting the design from unauthorized copying or reverse engineering.

Device Options and Packaging

The ACT 1 Series offers a selection of devices denoted by different part numbers, each differing in capacity and packaging types. Users can choose from devices with up to 273 flip-flops, and they provide several packaging options including PLCC, PQFP, VQFP, CPGA, and CQFP. Horizontal and vertical track resources are consistent across options, as is the number of PLICE antifuse elements.

Software Support

Supporting these FPGAs, Actel provides the Designer and Designer Advantage Systems software. These tools simplify logic design implementation and integrate with CAE systems. The software features include a windows-based GUI, schematic capture, simulation, automatic place and route, timing verification, device programming, VHDL optimization, and macro function generation for structural blocks.

Manual:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/a1020b-2pqg100c/-1509756069793380434/