The Z80 SIO Serial Input/Output Controller datasheet introduces a highly versatile and sophisticated dual-channel data communication interface designed primarily for Z80 family CPUs, but also suitable for a range of other CPUs. It operates on a single +5V power supply and incorporates a single-phase clock from the standard Z80 Family.

Key Features

The SIO supports a broad array of serial communication protocols, both asynchronous and synchronous, including standards like IBM’s BISYNC, SDLC HDLC, CCITT-X.25, and more. It allows data rates up to 500K bits/second using a 2.5MHz clock (28440 models) and up to 800K bits/second with a 4.0MHz clock (28440A models).

Each channel can operate fully independently, with features including:

- Complete message handling in 8-bit or variable-character formats

- Break generation and detection

- Error detection mechanisms for parity, overrun, and framing issues

- Automatic CRC generation and checking

- Buffered receiver and transmitter registers

- Highly efficient interrupt vectoring that does not require external logic

Design and Interfaces

The controller facilitates interfacing for CPU or DMA control and is capable of handling a wide variety of serial I/O tasks with both fast and slow peripheral devices. Its quad-buffered receiver data registers and doubly buffered transmitter registers allow for rapid data exchanges.

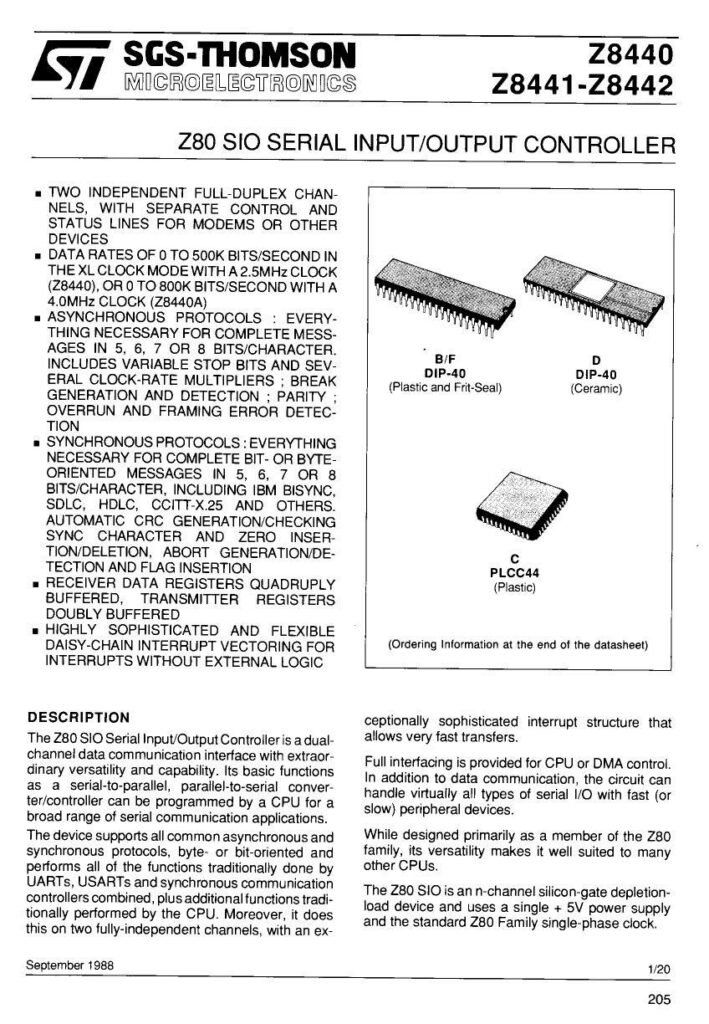

The datasheet details three available pin configurations: B/F DIP-40, DIP-40 (Ceramic and Plastic), and PLCC44 (Plastic), with specific pins described for handling functions such as data/command selection, system clock synchronization, and receiver and transmitter enabling. Notably, the Chip-Carrier package, identified as Z8444, is the preferred version for most applications due to its 44-pin configuration.

Interrupt Structure

The Z80 SIO boasts an advanced interrupt structure that permits swift data transfers and CPU alerts on logic level transitions. This is facilitated by the Schmitt-trigger buffering integrated into some inputs to accommodate slow-rise-time signals.

Ordering Information

Ordering details are provided at the end of the datasheet, directing users to options for obtaining the SIO.

Conclusion

The presented datasheet provides comprehensive information on the capabilities, design, and interfacing of the Z80 SIO for developers and engineers building and optimizing systems around the Z80 CPU ecosystem.

References:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/z8442bd2/7293076883943447758/