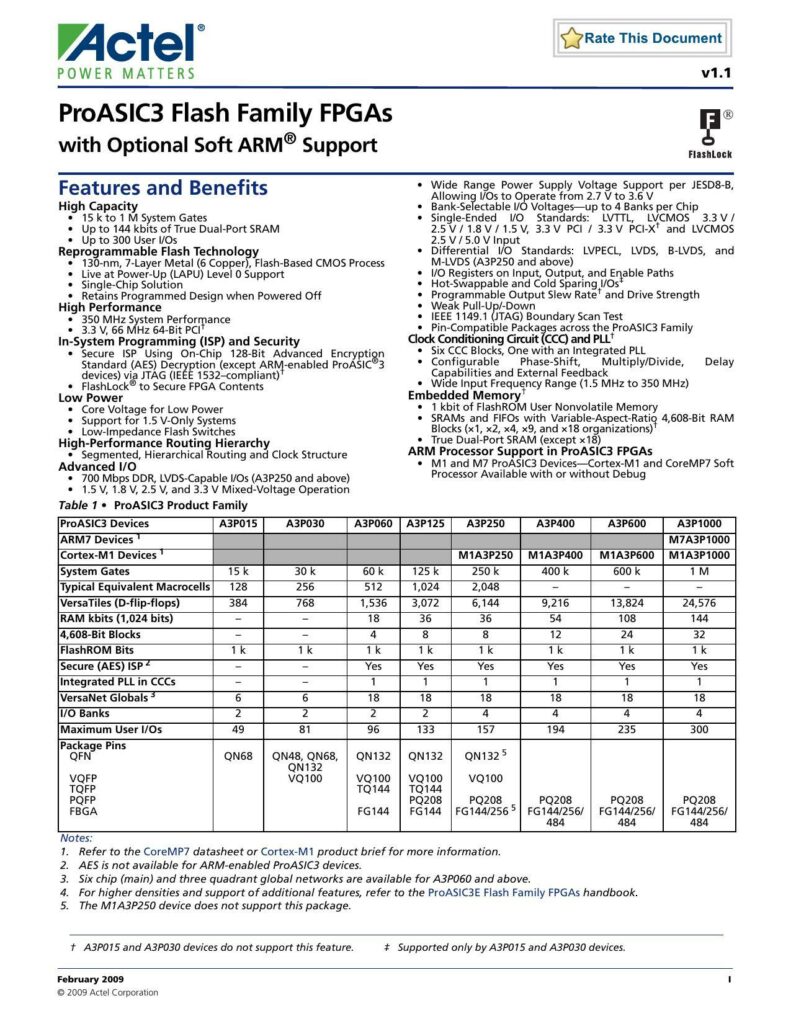

ProASIC3 FPGA Family Overview

Actel’s ProASIC3 Flash Family of Field Programmable Gate Arrays (FPGAs) provide a versatile and power-efficient solution suitable for a wide array of applications. With integrated features and benefits, they offer support for single-ended and differential I/O standards and come with varying system gate capacities. The datasheet covers various models, including the ARM-enabled devices, highlighting their memory, performance, and packaging options while addressing security through FlashLock and AES features.

Key Specifications:

– System Gates available from 15k to 1M.

– True Dual-Port SRAM up to 144 kbits and up to 300 User I/Os.

– Support for a wide range of I/O voltages and standards, including LVDS and PCI.

– In-System Programmable using 128-Bit AES encryption (excluding ARM devices).

– Live at Power-Up (LAPU), reprogrammable with high-performance Flash technology.

Advanced Features:

– High-performance routing hierarchy with segmented, hierarchical structure.

– Optional support for ARM processors such as Cortex-M1 and CoreMP7.

– Configurable output drive strength and slew rate.

– Integrated clock conditioning circuitry and up to six Clock Conditioning Circuit (CCC) blocks with one integrated Phase-Locked Loop (PLL).

– Compliance with JESD8-B standards for power supply voltage levels.

Security and Reliability:

– FlashLock technology ensures FPGA content security.

– Design retention following power-off with single-chip solution for resilient performance.

– Hot-swappable and sparing I/Os add to the FPGA’s robustness.

Product Family and Packaging Options

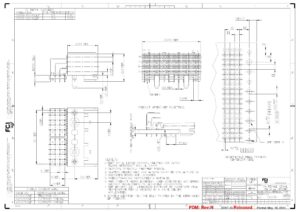

The ProASIC3 family includes a spectrum of devices ranging from A3P015 to A3P1000, and ARM-specific variants like M1ABP250 and ARM7-based MZABP1000, each varying in system gates and other features like embedded memory and I/O. The datasheet lists package and pin configurations alongside physical dimensions to aid in design considerations, with special notes on migration and compatibility for design flexibility.

Design and Migration Considerations

When transitioning to different density devices within the family, the datasheet encourages reference to the ProASIC3 Flash Family FPGAs Handbook. It also notes that differential I/O usage may affect the number of single-ended I/Os available. Additionally, some package sizes like FG256 and FG484 are footprint-compatible, facilitating easier upgrades or downgrades in device density.

References:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/a3p060-ftq144/-5663067958566585793/