Introduction

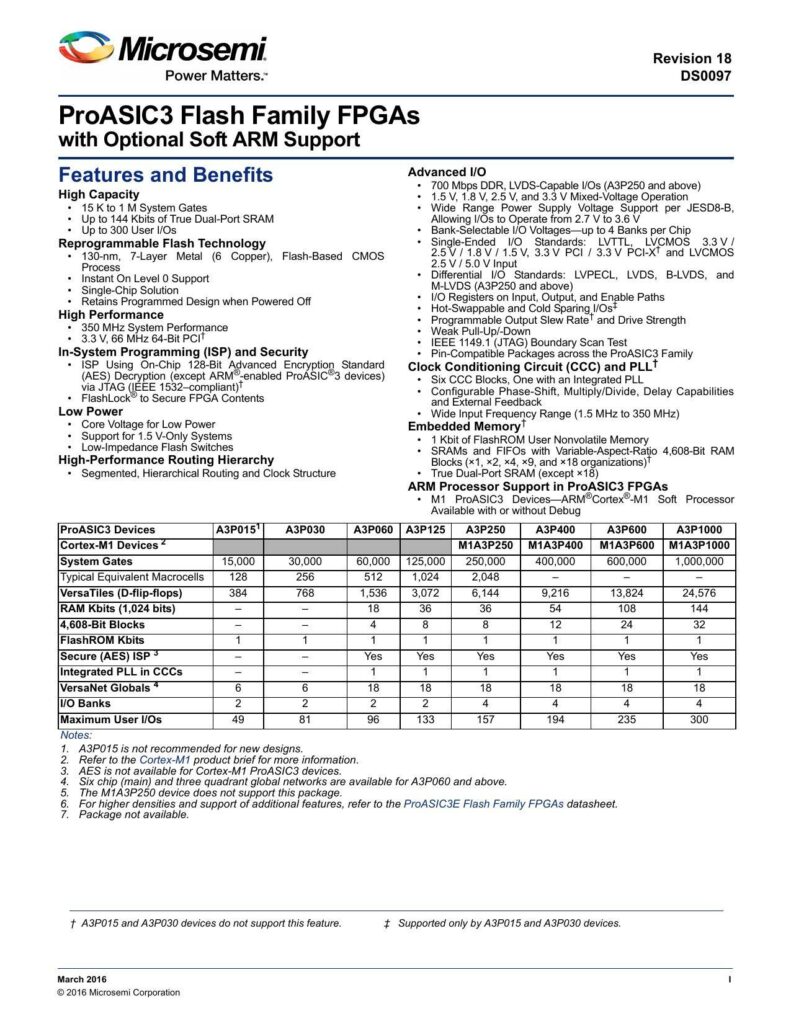

The Microsemi ProASIC3 Flash Family of Field Programmable Gate Arrays (FPGAs) offers a versatile range of devices equipped with optional soft ARM support. These devices are tailored for high-speed applications with capacities ranging from 15K to 1M system gates and providing up to 300 user I/Os.

Features

High-Speed Interfaces: The ProASIC3 devices boast advanced I/Os capable of 700 Mbps DDR and include LVDS options, supporting mixed-voltage operations (1.8V, 2.5V, and 3.3V).

Memory: The FPGAs feature up to 144 Kbits of true dual-port SRAM, with 4,608-bit RAM block organizations for high-performance routing. There is also embedded FlashROM user nonvolatile memory.

I/O Standards: ProASIC3 devices support a range of single-ended I/O standards, including LVTTL and LVCMOS, and differential standards like LVPECL and LVDS for devices A3P250 and above.

Programmability: The devices utilize reprogrammable Flash technology, with FlashLock® to secure FPGA contents. The in-system programmability is facilitated through JTAG.

System Support: This family includes pin-compatible packages across the range, offering a seamless upgrade path. ARM processor compatibility is included in ProASIC3 FPGAs with ARM Cortex®-M1 soft processors available in some models.

Performance: Supporting system performances up to 350 MHz, these FPGAs have configurable phase-shift, multiply/divide, delay capabilities and provide an Instant On Level 0 support for efficient use.

Clock Conditioning and Security: The FPGAs integrate a clock conditioning circuit with up to six CCC blocks, one with an integrated Phase-Locked Loop (PLL). They also provide AES decryption for added security (except for ARM-enabled devices).

Device Range and Configurations

The ProASIC3 family covers a range of devices with system gate counts from 15,000 to 1,000,000 and corresponding equivalent macrocells and VersaTiles for flexible design implementation. These devices are provided with varying RAM and FlashROM capacities to suit varying application requirements. Packages not available include A3P015 and A3PO30 devices, with certain features either supported only by A3PO15 and A3PO30 or excluded from those models.

Additional Considerations

The datasheet notes suggest referring to the Cortex-M1 product brief for detailed information on ARM support and highlights that the A3P015 recommended for new designs. Users are also directed to the ProASIC3E Flash Family FPGAs datasheet for higher densities and additional features. The provided information is based on the latest revision as of March 2016 by Microsemi Corporation.

Manual:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/m1a3p1000-1fg256/2663992543712156324/