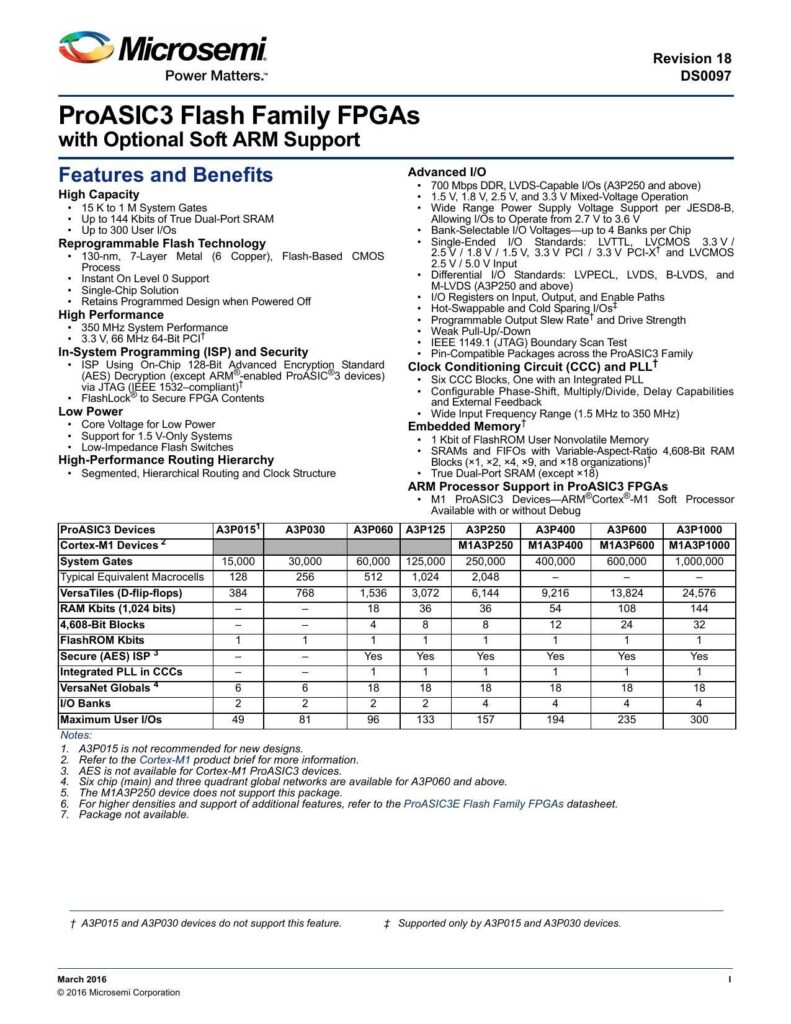

Microsemi ProASIC3 Flash Family FPGAs Summary

This datasheet provides detailed information on the ProASIC3 Flash Family of Field Programmable Gate Arrays (FPGAs) from Microsemi, highlighting their features and benefits, such as support for ARM processors and advanced I/O capabilities. The FPGAs are designed for a wide range of system gates, with capacities ranging from 15K to 1M, and various voltage operations including 1.5V, 1.8V, 2.5V, and 3.3V, accommodating mixed-voltage systems.

Key Features

The ProASIC3 devices boast high-capacity, with reprogrammable flash technology that retains programmed designs even when powered off. They offer up to 144 Kbits of True Dual-Port SRAM, up to 300 user I/Os, hot-swappable and cold sparing capabilities, In-System Programming (ISP), JTAG Boundary Scan Test support, low power consumption, and embedded memory, which is particularly beneficial for 1.5 V-only systems.

The datasheet notes support for a variety of I/O standards such as LVTTL, LVCMOS, PCI, and differential standards like LVPECL and LVDS. On the technical front, there’s the inclusion of a 130-nm, 7-layer Copper process, programmable output slew rate, and drive strength, as well as high-performance routing hierarchy with segmented, hierarchical routing and clock structures. It also features a Clock Conditioning Circuit (CCC) with up to six blocks, one of which includes an integrated Phase-Locked Loop (PLL).

ARM Processor and Security

ARM Cortex®-M1 soft processor support is available for ProASIC3 devices, with options for debug capabilities and a nod to security through the use of on-chip AES decryption. However, AES is not available for the ARM Cortex-M1 enabled ProASIC3 devices.

Product Variants and Packaging

The ProASIC3 line includes devices designated A3P015 to A3P1000, with corresponding Cortex-M1 variants. They come in a range of packages, including QFN, CS, VQFP, TQFP, PQFP, and FBGA types, each with differing pin options. Note that the A3P015 is not recommended for new designs and some features are not supported by certain lower density devices. For more advanced requirements, the ProASIC3E Flash Family FPGAs datasheet is recommended.

Additional Remarks

Additional notable features include FlashROM, SRAMs and FIFOs with variable-aspect-ratio RAM blocks, and maximum user I/O capacities, all selectively supported across different devices within the family. The document advises consulting the Cortex-M1 product brief for further information.

Important revisions and device specific notes are provided, such as lack of package support for specific models and recommendations to opt for alternative models for increased density and additional feature support. Furthermore, the intricate grid of global networks is available for A3P060 models and above, ensuring connectivity and performance.

References:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/a3p060-2tq144i/6332486339558221845/