Overview

The HIGH-SPEED IDT7005S/L is an 8K x 8 dual-port static RAM designed by Integrated Device Technology, Inc. It offers asynchronous operation, high-speed access, and full hardware support for semaphore signaling, making it optimal for applications requiring simultaneous reads and writes to the same memory location. Its key features include BUSY output/input flags, interrupt flags, on-chip port arbitration logic, and the capability for battery backup operation.

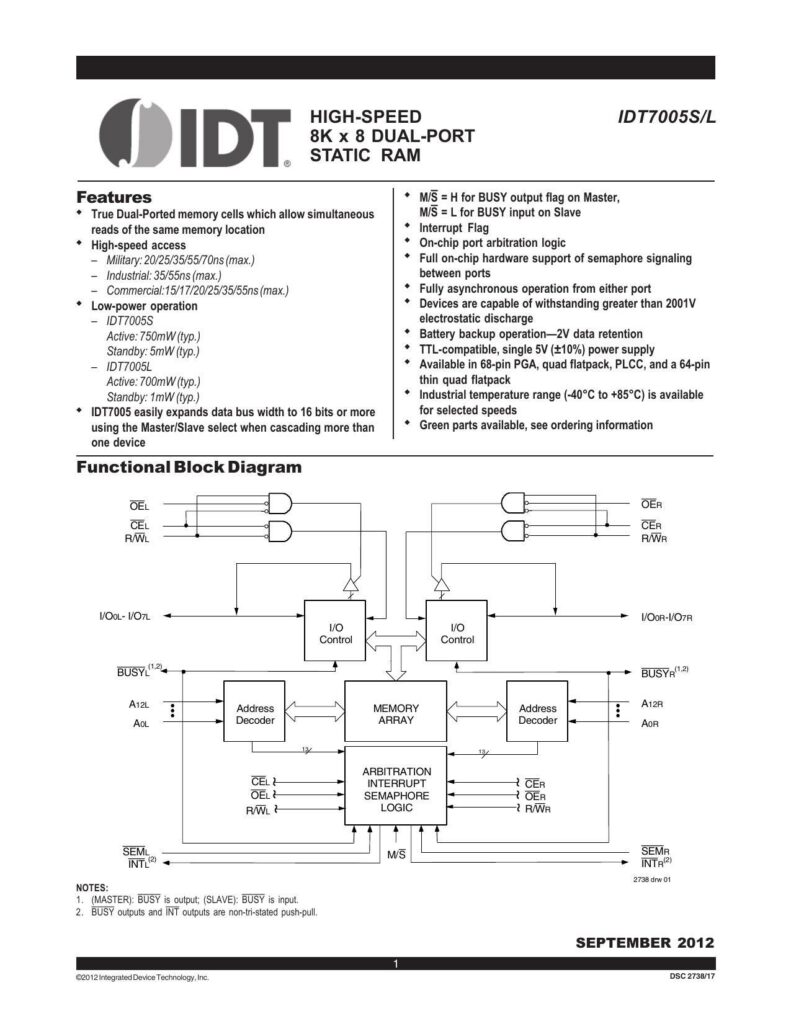

Features

This device has True Dual-Ported memory cells, facilitating concurrent access. Additionally, it has an on-chip arbitration logic system and provides built-in support for semaphore signaling. High-speed access is offered in various maximum speeds depending on the application environment, from 20ns to 70ns for military use, 35ns to 55ns for industrial use, and a much faster 15ns to 55ns for commercial applications.

Power Consumption

Featuring a low-power operation mode, the device’s typical active power consumption is 750mW for IDT7005S and 700mW for IDT7005L, while in standby it conserves power at 5mW for IDT7005S and 1mW for IDT7005L. It can also withhold electrostatic discharge greater than 2001V. These characteristics allow for enhanced energy efficiency and robust usability in various electrical environments.

Compatibility and Temperature Range

The RAM is TTL-compatible and operates with a single 5V (±10%) power supply. To serve a wide range of operational climates, an industrial temperature range from -40°C to +85°C is available. This flexibility ensures reliable performance across different deployment scenarios.

Packaging Options

Various packaging styles are available for this memory, including 68-pin PGA, quad flatpack, PLCC, and 64-pin thin quad flatpack. These configurations provide flexibility in hardware design considerations and are complemented by “green parts” as defined in the ordering information, reducing environmental impact.

Functional Elements

The functional block diagram in the datasheet reveals a well-structured internal architecture. This includes the memory array itself, address decoders, IO and VO control logic, and essential components for arbitration, semaphore, and interrupt handling (ARBITRATION, INTERRUPT, SEMAPHORE LOGIC). Additionally, the diagram denotes BUSY and INT outputs as non-tri-stated push-pull to ensure reliable communication states within the system.

Date and Publication

This datasheet was published as of September 2012, conveying the specifications at the time of release.

Ordering and Part Number Information

Specific part number and ordering details are likely included following the initial pages of the datasheet, directing users on how to procure the specific configurations suitable for their application.

References:

Download: HIGH-SPEED IDT7005S/L IDT 8K x 8 DUAL-PORT STATIC RAM

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/7005l55pf/3673612346744087830/