Description

The intersil Data Sheet introduces the X5328 and X5329 devices, which integrate three essential functions tailored for reliable system operations. These functions cover Power-on Reset Control, Supply Voltage Supervision, and Serial EEPROM Memory with Block Lock Protection. The integration of these features is designed to reduce overall system cost, save board space, and enhance reliability. When power is supplied, an onboard power-on reset circuit is activated, ensuring that the processor only begins executing code after power supply and oscillator have achieved stability.

Key Features

The document highlights several significant features of the X5328 and X5329 CPU Supervisors:

- Low Vcc detection with reset assertion ensures system stability by maintaining RESETIRESET when Vcc falls below a set voltage threshold.

- The device offers five standard reset threshold voltages and gives users the ability to reprogram the threshold, providing flexibility for custom requirements.

- RESET signal is guaranteed to be valid even when Vcc is as low as 1V.

- Efficiency is a focal point with the device’s low power consumption, boasting a <1μA maximum standby current, and <400μA during active EEPROM read operations.

- Includes 32Kbits of EEPROM Memory with built-in write protection to prevent unintended data alterations during power-up and power-down events.

- Block Lock protection enables varying levels of memory protection, from none to complete protection of the EEPROM array.

- EEPROM programming is streamlined with a ROM mode that’s in-circuit programmable, and a 32-byte page write mode to minimize programming time.

- Features a self-timed write cycle with a typical duration of 5ms and a 2MHz SPI interface compatible with modes (0,0 and 1,1).

- Versatility in power supply options, supporting 2.7V to 5.5V and 4.5V to 5.5V.

- The devices are available in multiple package options, including 14 Ld TSSOP, 8 Ld SOIC, and 8 Ld PDIP, all of which comply with RoHS.

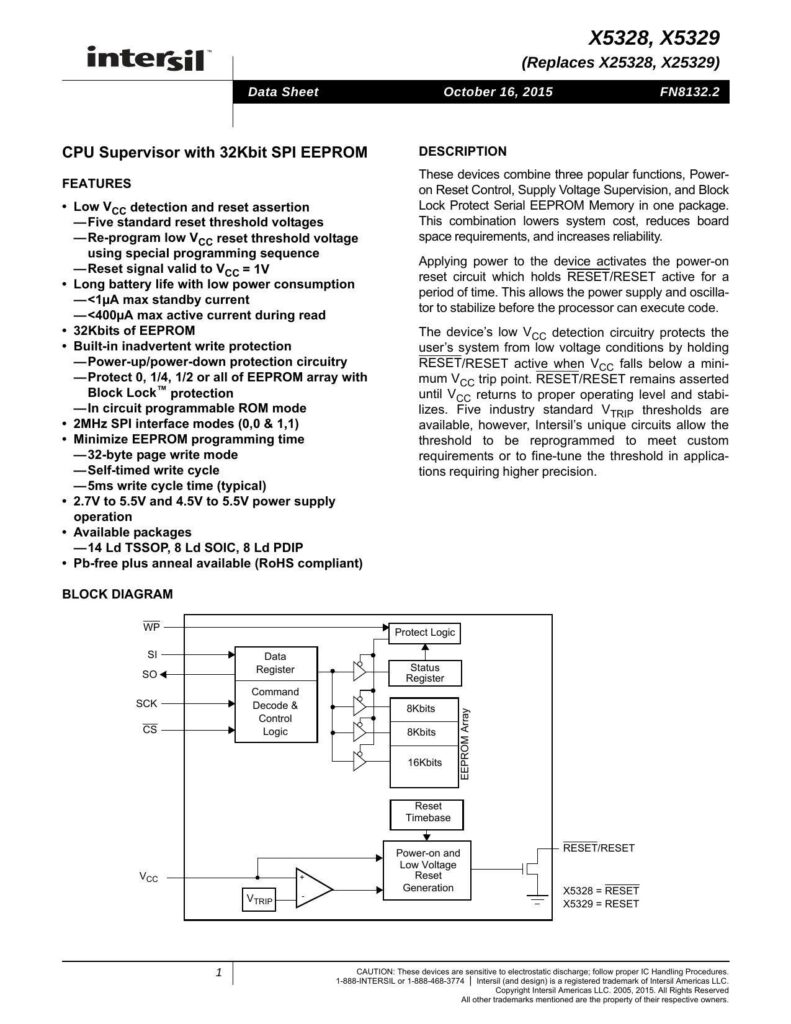

Block Diagram Overview

The block diagram included in the datasheet demonstrates the internal structure of the CPU Supervisors, featuring individual blocks for Protect Logic, Data Register, Status Register, Command Decode & Control Logic, and Reset Timebase. It illustrates connections to external SO and SCK signals, RESET/IRESET, WP, and Vcc, and showcases the division of EEPROM memory into segments totaling 32Kbits.

Caution

Finally, a note of caution is added to inform users that the X5328 and X5329 are sensitive to electrostatic discharge, advising adherence to proper Integrated Circuit (IC) Handling Procedures.

References:

Download: CPU Supervisor with 32Kbit SPI EEPROM

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/x5329s8iz-4-5a/2065570707641926841/