Overview

The 74F244/74F244B Octal Buffers (3-State) datasheet provides detailed specifications for Philips Semiconductors’ line of octal bus interface 3-State output buffers designed for driving bus lines or buffer memory address registers. These devices are particularly well-suited to applications that require high sink current capabilities and good capacitive drive characteristics.

Features

The 74F244 can source up to 15mA current and sink 64mA, delivering strong performance in driving bus lines. Notably, the 74F244B version introduces several enhancements over the standard 74F244, such as reduced ground bounce, reduced supply current consumption (Icc), minimized output skew (< 2.0ns), lower input leakage current (Iil), and improved noise immunity due to a split lead frame. Additionally, an industrial temperature range option is available, extending from -40°C to +85°C. For packaging, the 74F244 is offered in a SSOP Type II format.

Description

Equipped with two output enables, OEa and OEb, the 74F244/74F244B control four 3-State outputs each. The functionality remains unchanged between the 74F244 and the 74F244B model, with the latter designed to mitigate ground noise effects and offer additional benefits as mentioned in its features.

Performance Specifications

The devices exhibit a typical propagation delay of 4.0ns, alongside varied typical supply currents: the 74F244 consumes approximately 53mA, whereas the 74F244B is more energy-efficient at 33mA.

Ordering Information

Different order codes are available depending on temperature ranges and packaging requirements. The commercial range models, specified for 0°C to +70°C, and the industrial range models, specified for -40°C to +85°C, have suffixes ‘N’ and ‘D’ for plastic DIP and plastic SOL packages, respectively. A plastic SSOP II package is also indicated with ‘DB’. Part numbers also distinguish between the standard and the ‘B’ variant of the product.

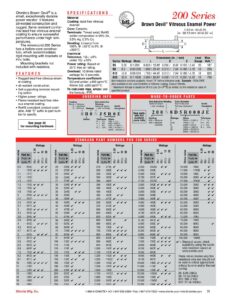

Input and Output Loading and Fan-Out Table

The datasheet includes a detailed table for both versions, explaining load values optimized for high and low states, and specifies current values for various pins such as data inputs (lan, Ibn), output enable inputs (OEa, OEb), and data outputs (Yan; Ybn).

Note:

One FAST unit load is defined as 20µA in the high state and 0.6mA in the low state, used as reference for the loading values.

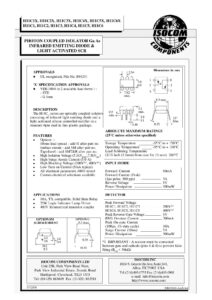

Pin Configuration and Logic Symbol

Diagrams for pin configuration and logic symbol are provided to assist in the understanding of physical layout and logical operation. The pin configuration displays the arrangement of data inputs, output enables, data outputs, VCC, and GND pins. The logic symbol graphically represents the logical connections and functions of each pin.

Manual:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/n74f244n/-4922962066669778907/