Overview

The X28HC256 is a high-performance CMOS EEPROM (Electrically Erasable Programmable Read-Only Memory), featuring a 32k x 8 memory organization. This second-generation device is constructed with Intersil’s specialized textured poly floating gate technology, ensuring a reliable nonvolatile memory solution operating at 5 volts. It stands out for its 128-byte page write operation, which enables a rapid write process of approximately 24µs per byte, thus allowing the full memory capacity to be overwritten in under 0.8 seconds. Additionally, users can monitor write progression through two early end-of-write detection methods: DATA polling and Toggle bit polling. For added security during write operations, the EEPROM includes a JEDEC standard software data protection mechanism.

Key Features

The X28HC256 EEPROM comes with an array of features designed to ensure ease of use, efficiency, and reliability:

- Fast Access Time: The memory offers a quick access time of 90ns.

- Efficient Writing: It supports byte and page writing operations without the need for a prior erase step.

- Single 5V Supply: The device functions solely on a 5V power supply, negating the need for external high voltage sources.

- Self-Timing Write Cycle: It manages write cycles with its built-in timing mechanisms, ensuring ease of programming.

- Low Power Consumption: The device operates at 60mA when active and a mere 500µA in standby mode.

- Software Data Protection: This feature guards against unintentional writes, enhancing data security during power transitions.

- High Speed Page Write Capability: The EEPROM is capable of quick page write operations for efficient data management.

- Endurance and Retention: It is rated for a minimum of 100,000 write cycles per byte with a data retention period of 100 years.

- RoHS Compliant: The EEPROM conforms to the Restriction of Hazardous Substances (RoHS) directive, making it environmentally friendly.

Applications and Functionality

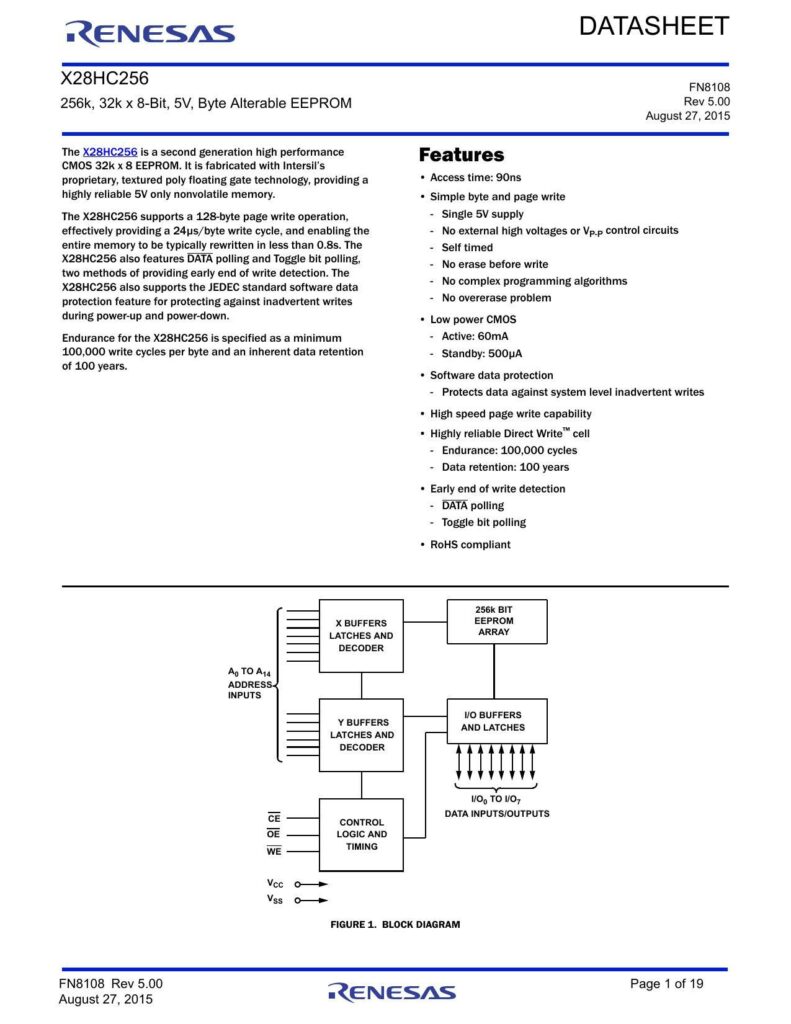

The block diagram provided on the datasheet indicates the internal architecture, which includes an EEPROM array, buffers, latches, decoders, address inputs (Ao to A14), data inputs/outputs (IOo to IOz), control logic and timing, and power supply pins (Vcc, Vss). These components are interfaced via control lines for Chip Enable (CE), Output Enable (OE), and Write Enable (WE). The device’s architecture and the array of features make it suitable for a wide range of applications where reliable, low-power nonvolatile memory is crucial.

References:

Download: X28HC256 256k, 32k X 8-Bit; 5V, Byte Alterable EEPROM

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/x28hc256piz-12/7170738863784712967/