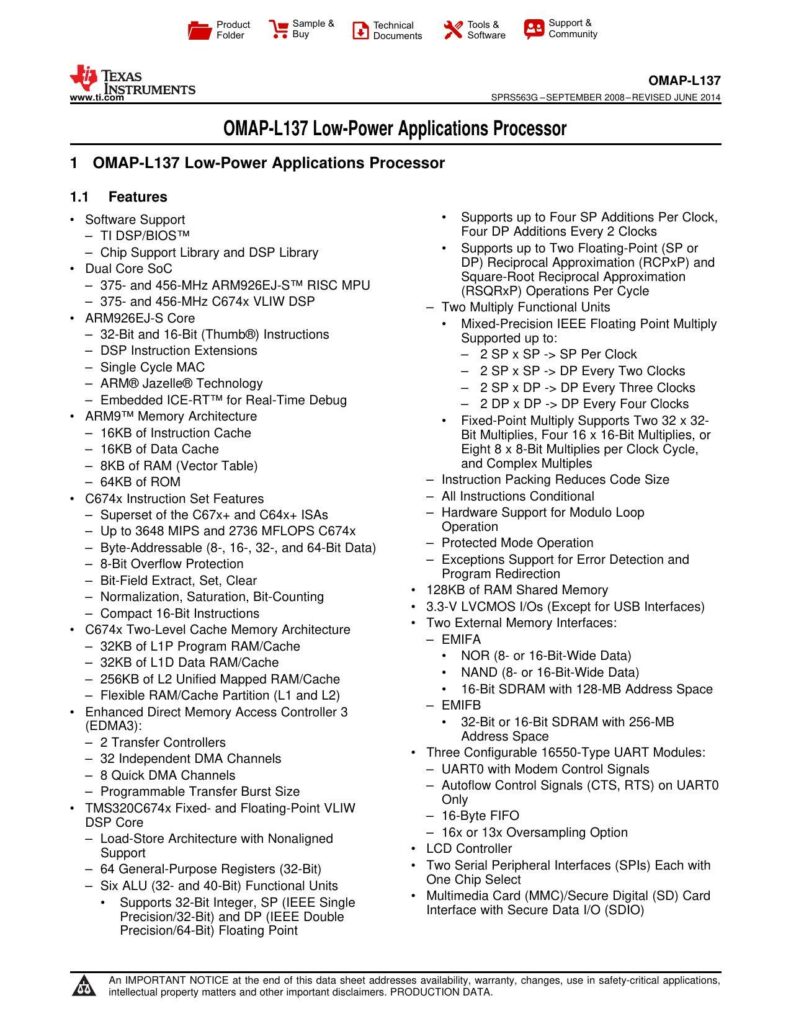

The OMAP-L137 is a low-power applications processor developed by TEXAS INSTRUMENTS, highlighted for its dual-core System on Chip (SoC) design. The first core is a 375- and 456-MHz ARM9Z6EJ-STM RISC MPU, and the second is a 375- and 456-MHz C674x Very Long Instruction Word (VLIW) Digital Signal Processor (DSP). The ARM926EJ-S core operates with standard 32-Bit and 16-Bit Thumb instructions while offering DSP instruction extensions, Single Cycle Multiply-Accumulate (MAC), and support for Jazelle technology for Java acceleration. Additionally, it features Embedded ICE-RT for real-time debugging and adheres to the ARM memory architecture, with various cache and memory allocations, including 16KB of instruction cache, 16KB of data cache, 8KB of RAM for vector tables, and 64KB of ROM.

The DSP component provides a robust set of features, including a comprehensive instruction set, compatibility supersetting both C67x+ and C64x+ ISAs, and performance capabilities up to 3648 MIPS and 2736 MFLOPS. The C674x DSP enables a variety of data types and protections, such as byte-addressable (8-, 16-, 32-, and 64-Bit) operations, 8-Bit overflow protection, and bit manipulation functionalities like field extract, set, clear, and counting. It supports compact 16-Bit instructions for efficient use of space.

Cache memory architecture within the C674x DSP is two-leveled, with 32KB of LIP Program RAMCache, 32KB of LID Data RAMCache, and 256KB of L2 Unified Mapped RAMCache. The user can flexibly partition RAMCache between L1 and L2 as needed. A key feature of the processor is the Enhanced Direct Memory Access Controller 3 (EDMA3) which includes two transfer controllers, 32 independent DMA channels, and 8 quick DMA channels with programmable burst sizes.

The processor’s DSP core is optimized for both fixed- and floating-point operations, with a load-store architecture that supports non-aligned data types. It houses 64 general-purpose 32-Bit registers and includes functional units for arithmetic and algebraic operations. It can handle multiple floating-point operations per clock cycle and various fixed-point multiplications with precision choices, thus ensuring high processing efficiency.

The OMAP-L137 facilitates numerous interfaces and peripherals which include two external memory interfaces, multiple UART modules with modem and autoflow control signals, a liquid crystal display (LCD) controller, two Serial Peripheral Interfaces (SPIs) with chip select options and a Multimedia Card/Secure Digital (MMC/SD) card interface which supports secure data I/O.

All these features are combined into a single processor designed for low-power applications, making it suitable for a wide range of products and technological solutions. It concludes with an important notice regarding the product’s availability, warranty, changes, usage in safety-critical applications, intellectual property matters, and other disclaimers that users should be aware of.

References:

Download: OMAP-L137 Low-Power Applications Processor

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/omapl137bzkb3/-2441244165828594617/