ProASIC3L Low Power Flash FPGAs Overview

The datasheet provides extensive details about the ProASIC3L family of low-power Flash Field-Programmable Gate Arrays (FPGAs) featuring Flash*Freeze technology developed by Microsemi. The FPGAs are designed to cater to applications requiring single-ended and differential I/O standards, along with low power consumption. These devices support various voltage levels for LVTTL, LVCMOS, and are PCI compliant.

Key Features and Benefits

The datasheet showcases various features, including a wide range of supported I/O standards such as LVPECL, LVDS, B-LVDS, and M-LVDS. These FPGAs come with a significant reduction in dynamic and static power usage. Furthermore, they offer support for voltage-referenced IIO standards like GTL and HSTL. Other notable features include: up to 3,000,000 system gates, up to 504 kbits of true dual-port SRAM, programmable output slew rate, hot-swappable I/Os, and advanced clock conditioning circuitry with PLLs.

Power Supply and Performance

Devices within the ProASIC3L family are operable across a wide range of power supply voltages, complying with JESD8-B and JESD8-12 specifications, thus enabling them to operate between 2.7V and 3.6V. The FPGAs offer high system performance of 350 MHz for 1.5 V systems and 250 MHz for 1.2 V systems, and support in-system programming and security features, boasting a robust security framework provided by AES decryption via JTAG.

Resource Allocation and Device Options

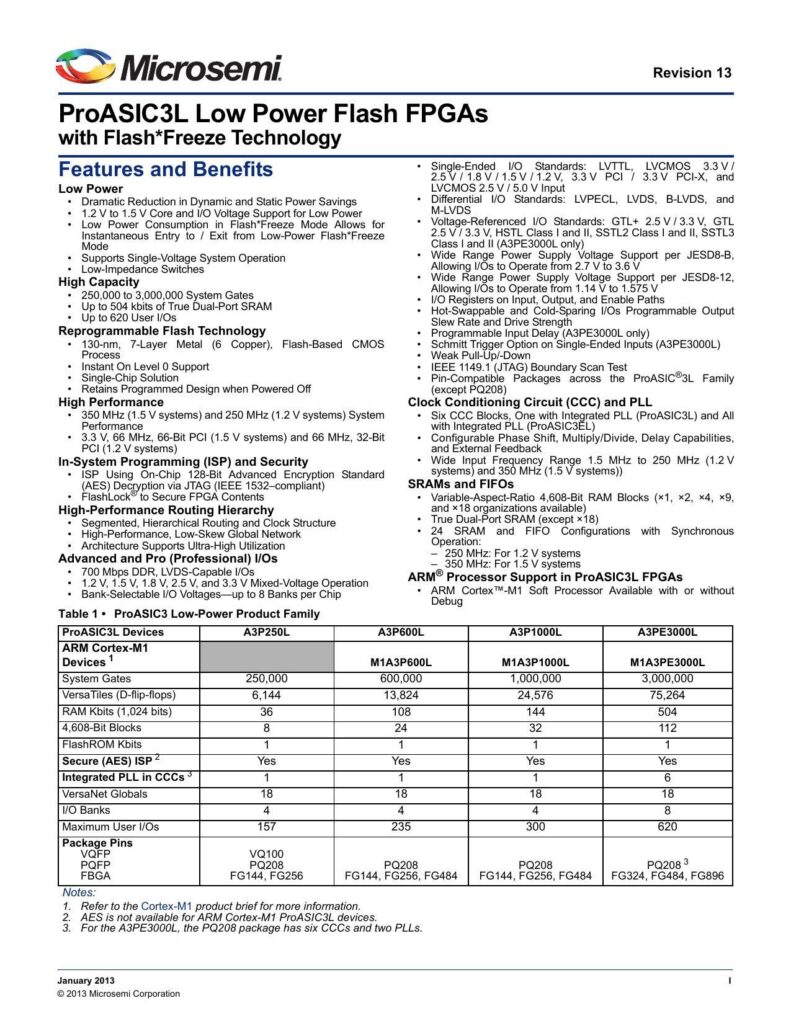

Table 1 in the datasheet lists the ProASIC3 Low-Power Product Family, including various device options such as A3P250L, A3PGOOL, A3P1OOOL, and A3PE3OOOL, as well as ARM Cortex-M1 based devices. These options range from 250,000 to 3,000,000 system gates, offering flexibility in the selection of FPGA resources for different applications. Version upgrades, packaging options, available user I/Os, and RAM configurations are detailed for each device.

Packaging Details and Design Considerations

The datasheet’s second page focuses on the packaging details such as package sizes and the number of I/Os per package. Various form factors are provided, including VQFP, PQFP, and FBGA, with dimensions and pin counts tailored for easy integration into various systems. The note section reminds designers of I/O pair limitations and compatibility between packages to assist in design and board migration planning.

Optimization for Search Engines

The summary has been crafted to include key specifications and industry terminologies such as “Flash*Freeze technology,” “low power,” “dynamic and static power savings,” “IIO standards,” and “AES security,” allowing better visibility and relevance for search queries related to FPGAs and their features.

References:

Chat: Powered By VoiceSphere

Pricing & Distributors: https://www.datasheets360.com/part/detail/m1a3pe3000l-fg896/-428162882542882722/